- Untuk memahami karakteristik rangkaian gerbang logika

- Untuk mengetahui bagaimana cara merangkai rangkaian gerbang logika

- Dapat mensimulasikan rangkaian gerbang logika

1. Gerbang Logika NAND

Contoh: IC 7400

IC 7400 merupakan ic yang dibangun dari gerbang logika dasar NAND. Gerbang NAND menghendaki semua inputnya bernilai 0 (terhubung dengan ground) atau salah satunya bernilai 1 agar menghasilkan output yang berharga 1.

Spesifikasi IC 7400:

- Tegangan Suply : 7 V

- Tegangan Input : 5.5 V

- Beroperasi pada suhu udara 0 sampai +70 derajat

- Kisaran suhu penyimpanan : -65 derajat sampai 150 derajat celcius

Konfigurasi pin:

- Vcc : kaki 14

- GND : kaki 7

- Input : kaki 1 dan 2,4, dan 5,13 dan 12, 10 dan 9

- Output : kaki 3, 6, 1

2. Logicstate

Gerbang Logika (Logic Gates) adalah sebuah entitas untuk melakukan pengolahan input yang berupa bilangan biner (hanya terdapat 2 kode bilangan biner yaitu, angka 1 dan 0) dengan menggunakan Teori Matematika Boolean sehingga menghasilkan sebuah sinyal output yang dapat digunakan untuk proses berikutnya.

3. Resistor, berfungsi sebagai pembagi, pembatas, dan pengatur arus dalam suatu rangkaian.

Resistor

merupakan salah satu komponen elektronika pasif yang berfungsi untuk

membatasi arus yang mengalir pada suatu rangkaian dan berfungsi sebagai

terminal antara dua komponen elektronika. Tegangan pada suatu resistor

sebanding dengan arus yang melewatinya

Resistor berfungsi untuk menghambat arus dalam rangkaian listrik. Cara menghitung nilai resistansi resistor dengan gelang warna:

1. Masukan angka langsung dari kode warna gelang pertama.

2. Masukan angka langsung dari kode warna gelang kedua.

3. Masukan angka langsung dari kode warna gelang ketiga.

4. Masukkan jumlah nol dari kode warna gelang ke-4 atau pangkatkan angka

tersebut dengan 10 (10^n), ini merupakan nilai toleransi dari

resistor.

4. LED

pinout:

Light

Emitting Diode atau sering disingkat dengan LED adalah komponen

elektronika yang dapat memancarkan cahaya monokromatik ketika diberikan

tegangan maju. Cara

kerjanya pun hampir sama dengan Dioda yang memiliki dua kutub yaitu

kutub Positif (P) dan Kutub Negatif (N). LED hanya akan memancarkan

cahaya apabila dialiri tegangan maju (bias forward) dari Anoda menuju ke

Katoda.LED

terdiri dari sebuah chip semikonduktor yang di doping sehingga

menciptakan junction P dan N.

spesifikasi:

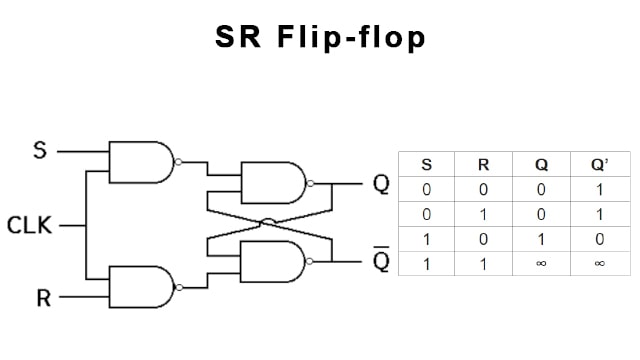

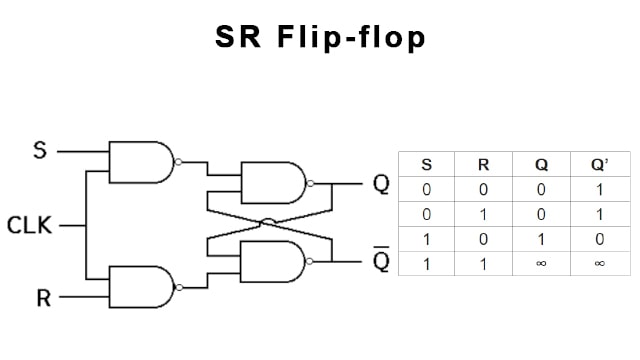

RS Flip Flop ini adalah dasar dari semua Flip-flop yang memiliki 2 gerbang inputan / masukan yaitu R dan S. R artinya “RESET” dan S artinya “SET”. Flip-flop yang satu ini mempunyai 2 keluaran / outputyaitu Q dan Q`. Disini kita akan membahas Level-Triggered and Edge-Triggered Flip-Flop.

Edge-triggered flip-flop, yaitu untai flip-flop

yang mempunyai input sinyal clock, dan output akan bereaksi terhadap

perubahan input saat sinyal clock berubah dari 0 ke 1 (untuk tipe

Positive-Edge-Triggered FF) atau saat clock berubah dari 1 ke 0 (untuk tipe Negative-Edge-Triggered FF).

Dalam flip - flop yang dipicu level, output merespons data yang ada pada input selama waktu level pulsa clock TINGGI (atau RENDAH). Artinya, setiap perubahan pada masukan selama jam aktif (TINGGI atau RENDAH) tercermin pada keluaran sesuai tabel fungsinya. Flip-flop R-S clock yang dijelaskan di paragraf sebelumnya adalah flip-flop pemicu level yang aktif saat clock HIGH.

Pada flip-flop yang dipicu edge, output merespons data pada input hanya pada transisi RENDAH-ke-TINGGI atau TINGGI-ke-RENDAH dari sinyal clock. Flip - flop dalam dua kasus ini masing - masing disebut sebagai edge trigger positif dan edge trigger negatif. Setiap perubahan input selama pulsa clock TINGGI (atau RENDAH) tidak berpengaruh pada output. Dalam kasus tepi memicu flip-flop, sebuah rangkaian detektor tepi mengubah masukan jam menjadi pulsa yang sangat sempit yang beberapa nanodetik lebar. Pulsa sempit ini bersamaan dengan baik RENDAH-ke-TINGGI atau TINGGI-ke-RENDAH transisi input jam, tergantung pada apakah itu adalah flip-flop yang dipicu sisi positif atau flip-flop yang dipicu sisi negatif. Pulsa ini begitu sempit sehingga pengoperasian flip - flop dapat dianggap telah terjadi pada tepi itu sendiri.

Tabel Kebenaran SR Flip-Flop:

Example

1. Buatkan gambar rangkaian RS flipflop aktiv high input

beserta tabel kebenarannya

Jawab:

2. Buatkan tabel kebenaran outputnya dari gambar rangkaian di

bawah

Jawab:

Problem

1. pada gambar rangkaian di bawah apa yang terjadi jika input

SET dan RESET nya berlogika 0 (LOW) ?

Kondisi input (yaitu R = S = 0) yang menyebabkan situasi

seperti itu dianggap sebagai kondisi yang tidak valid dan dilarang.SET = RESET

= 0 dilarang karena kondisi seperti itu mencoba mengatur (yaitu, Q = 1) dan

mengatur ulang (yaitu, Q = 1) flip-flop pada saat yang bersamaan. Untuk lebih

tepatnya, input SET dan RESET di R-S flip-flop tidak dapat aktif pada saat yang

bersamaan.

2. Bagaimana

fungsi clock dalam gambar rangkaian di bawah?

Jawab:

Dalam flip-flop yang dipicu level, output merespons data

yang ada di input selama level pulsa clock TINGGI (atau RENDAH). Artinya,

setiap perubahan pada input selama jam aktif (TINGGI atau RENDAH) tercermin

pada output sesuai tabel fungsinya. Flip-flop R-S clock yang dijelaskan dalam

paragraf sebelumnya adalah flip-flop yang dipicu level yang aktif ketika jamnya

TINGGI

Pilihan Soal Ganda

1. Salah satu cara yang data dilakukan agar output 1Q berlogika

1 adalah...

a. Seluruh

input harus berlogika 0

b. Menunggu/mengubah

Input 1S1 berdetak dari 0 ke 1 kemudian kembali menjadi 0

c. Tidak

ada cara yang dapat mengubah output IC tersebut

d. Menambahkan

LED pada output IC

Jawaban : b

2. Bagaimana agar output dari rangkaian di bawah ini

berlogika 1?

a. Q akan

berlogika 1 (HIGH)

b. Q akan

berlogika 1 (HIGH)

c. Q

dan Q akan berlogika 1 (HIGH)

d. Forbidden

Jawaban : b

4. Percobaan [Kembali]

a. Prosedur Percobaan

Pada percobaan kali ini dilakukan dengan prosedur sebagai berikut:

- Mempersiapkan Alat beserta Bahan seperti yang telah tertera pada Sub Bab Alat dan Bahan di atas

- Merangkai Rangkaian sesuai dengan jenisnya masing-masing, terdapat 1 jenis rangkaian yang akan diujikan.

- Pada Rangkaian dihubungkan input set dan reset dengan clock (sinyal pulsa) agar dapat melihat bagaimana output yang didapatkan.

- Amatilah nilai input dan output dengan menyesuaikannya dengan tabel kebenaran yang ada, dan juga amatilah hasil dari input dan outputnya.

b. Rangkaian Simulasi dan Prinsip Kerja

10.23 rangkaian flip flop edge triggered ini terjadi ketika diberi sinyal pulsa (clock) yang akan bernilai 1 (HIGH), dimana akan ada beberapa macam bentuk yang terjadi.

- Ketika Set Aktif, maka set akan bernilai 1 dan reset bernilai 0.

Saat Set diumpankan dengan clock yang berlogika 1 pada gerbang logika NAND, maka akan terjadi perkalian yang menghasilkan 1 lalu dilakukan pembalikan sehingga menghasilkan 0. kemudian akan diteruskan ke kaki NAND berikutnya nilai 1. Kemudian pada reset yang bernilai 0 akan dikalikan dengan clock bernilai 1 lalu dibalikkan sehingga akan menghasilkan 1 lalu diteruskan ke gerbang logika NAND berikutnya. Pada Rangkaian nanti akan diperlihatkan nilai output Q bernilai 1. nilai Q ini akan diumpankan ke gerbang logika kedua reset yaitu Q bernilai 1 dikalikan dengan nilai 1 lalu dibalikkan sehingga dihasilkan 0. ini memperlihatkan bahwa sinyal aktif pada set sehingga hanya pada set arus mengalir.

- Ketika Reset Aktif, maka reset akan bernilai 1 dan set bernilai 0.

Saat Reset diumpankan dengan clock yang bernilai 1 pada gerbang logika NAND,

maka akan terjadi perkalian yang menghasilkan 1 lalu dilakukan

pembalikan sehingga menghasilkan 0. kemudian akan diteruskan ke kaki

NAND berikutnya nilai 1. Kemudian pada set yang bernilai 0 akan

dikalikan dengan clock bernilai 1 lalu dibalikkan sehingga akan

menghasilkan 1 lalu diteruskan ke gerbang logika NAND berikutnya. Pada

Rangkaian nanti akan diperlihatkan nilai output Q bergaris bernilai 1. nilai Q

bergaris ini akan diumpankan ke gerbang logika kedua set yaitu Q bernilai 1

dikalikan dengan nilai 1 lalu dibalikkan sehingga dihasilkan 0. ini

memperlihatkan bahwa sinyal aktif pada reset sehingga hanya pada reset arus

mengalir.

- Ketika Set dan Reset Aktif, maka keduanya bernilai 1.

Saat Keduanya aktif dan sinyal pulsa juga dimasukkan bernilai 1. Maka, ketika diumpankan ke kedua gerbang NAND akan menghasilkan yang sama sama 0. Nantinya, hasil dari Q dan Q bergaris tidak akan terdefinisi karena semuanya aktif namun arus tetap mengalir pada keduanya.

c. Video

Download HTML silahkan klik Disini

Download Datasheet Resistor silahkan klik Disini

Download Datasheet LED silahkan klik Disini

Download Datasheet Gerbang NAND (IC7400) silahkan klik Disini

Download bentuk rangkaian 10.23 silahkan klik Disini

Download video simulasi rangkaian 10.23 silahkan klik Disini

.png)

.png)

.png)